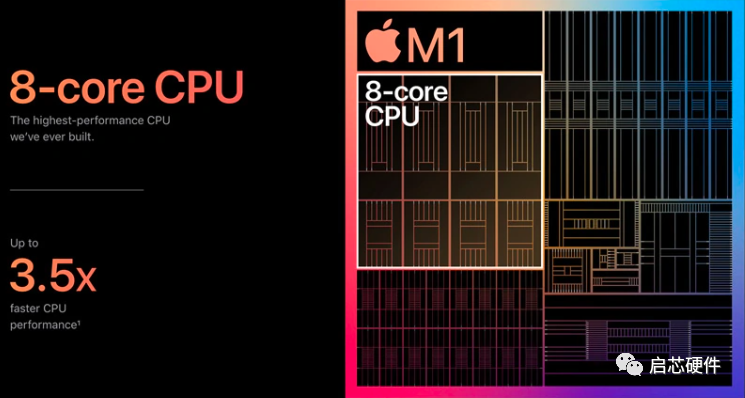

这颗芯片采用台积电5纳米制程工艺,CPU、GPU、缓存集成在一起,拥有8核CPU(其中4颗为高性能核心,另外四颗为高能效核心),8核GPU,其中包含160亿个晶体管。

苹果M1的核心参数详细如下,可以根据后面Floorplan进行交叉核对

项目

参数

CPU

核心数:8核频率信息:4×3.2GHz Firestorm+4×2.064GHz Icestorm

GPU

核心数:8核(部分机型为7核)

晶体管

约160亿个

架构

Arm架构

制程

5纳米

接口

集成雷电/USB 4控制器、PCle 4.0控制器、NVMe存储

安全模块

Secure Enclave

机器学习加速器

集成

ISP

集成

音频处理器

集成

性能控制器

集成

加密加速器

集成

神经网络引擎

16核

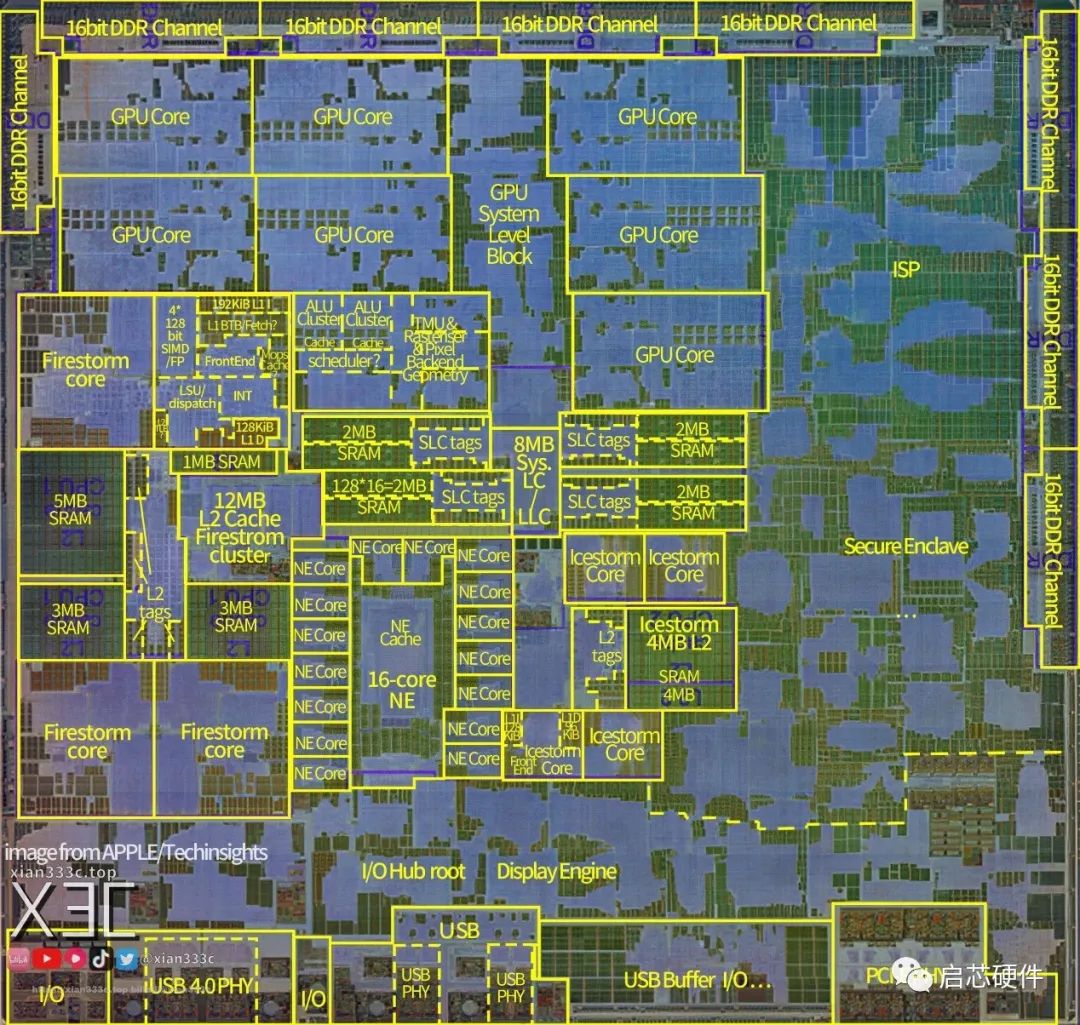

Apple M1芯片 floorplan分析

下面是Apple M1芯片的floorplan, 以及各模块的分析

Floorplan的基本分析:

1.内存一共128 bit, 一共8个通道,接口在上方和右边,最左边是1个16bit DDR channel, 上面是4个16bit DDR channel, 右边有3个16bit DDR channel。这样DDR phy的摆放,能确定肯定不是PoP封装的,颗粒肯定是放在上方或右边,如下图所示;

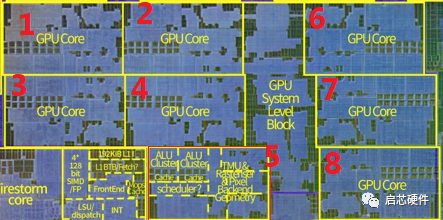

2.内存颗粒的下方是GPU core, 如下图,其中core 5有GPU core里面的详细组成单元

3.再往下是CPU CORE 4+4组成,如下图,4个大核firestone core,4个小核icestorm core

4.而16个神经网络引擎夹杂在大小核心中间,如上图所示。system cache, SLC相关的东西在就在NE网络的上面,如上图。

5.South方向,是高速串行接口,如usb 4.0, usb buffer, PCIe phy相关的IP, 以及视频引擎。

6.在East方向,除了LPDDR的模组,靠内侧就是ISP模块占据了大块die size, 其下方就是secure enclave, 同样占据了大片die size。这两块跟上一代芯片类似

各模块的面积密度分析

M1

area(mm^2)

size(MiB)

SRAM density(MB/mm^2)

Firestorm L2

3.500539165

12

3.428043348

Icestorm L2

1.228958081

4

3.254789614

SLC

2.45910606

8

3.253214707

TSMC 5nm HP

3.688064141

12

3.253739507

TSMC 5nm HD

3.500539165

12

3.428043348

total

7.188603306

24

3.338617945

最后,是各种同类型芯片的SRAM 密度和relative upshift的对比,能更直观看到差异。

M1

(TSMC 5nm HD)

M1

(TSMC 5nm HP)

A14

(TSMC 5nm HD)

SRAM density

3.428043348

3.253739507

3.669986689

Relative upshift

0.00%

5.36%

-6.59%

A14

(TSMC 5nm HP)

Lakefield

(Intel 10nmSF)

SD855

(TSMC 7nm DUV HD)

SRAM density

3.35286302

1.675987565

2.463892974

Relative upshift

2.24%

104.54%

39.13%

K980

(TSMC 7nm DUV HD)

KX5000

(HLMC 28nm)

SRAM density

2.386652552

0.407069712

Relative upshift

43.63%

742.13%

总结分析:

1.M1芯片的芯片尺寸约为120.5mm²

2.M1采用台积电的5纳米工艺,其在密度方面取得了巨大的提升(大约比7纳米提高了35-40%),在某些情况下甚至看起来更好。

3.而7纳米工艺在某些情况下仍然保持在每平方毫米约1.6MB的水平,这种情况下,5纳米工艺可以实现100%的密度提升。